Full Cycle Design of Integrated Circuits

Own design center for digital integrated circuits and functional blocks from RTL to GDS;

Development of architectural solutions;

Development and functional verification of functional blocks;

HDL integration assembly of the project, functional verification;

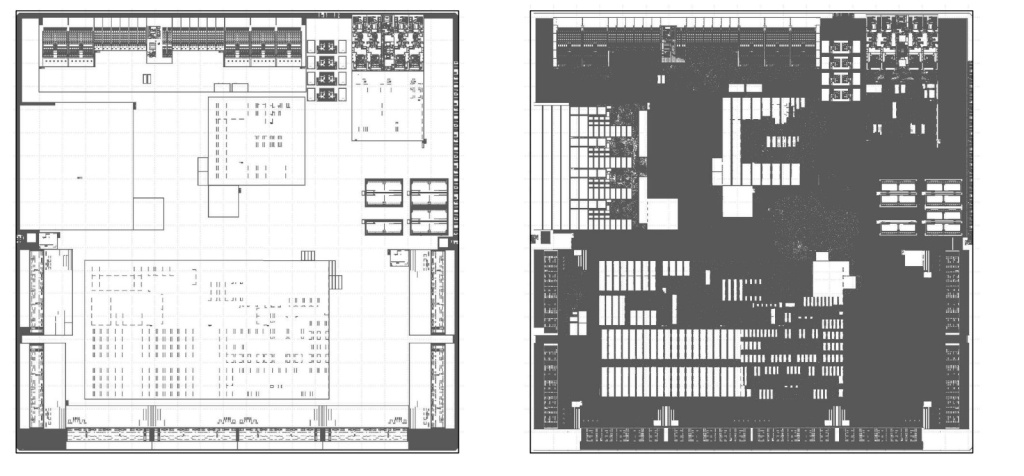

Front End design – logical synthesis and formal verification;

Back End design – topological synthesis DRC, LVS, DFM.

Manufacturing

Fabrication of chips, assembly into packages, logistics;

Fabrication of mask sets, wafers, factory testing.

FPGA Development

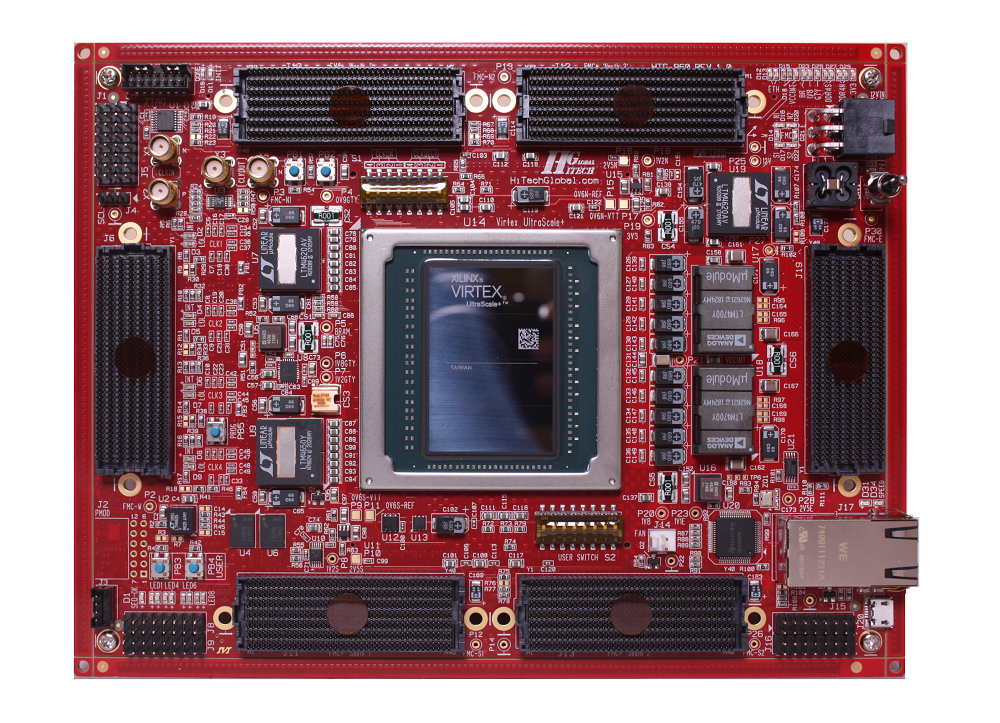

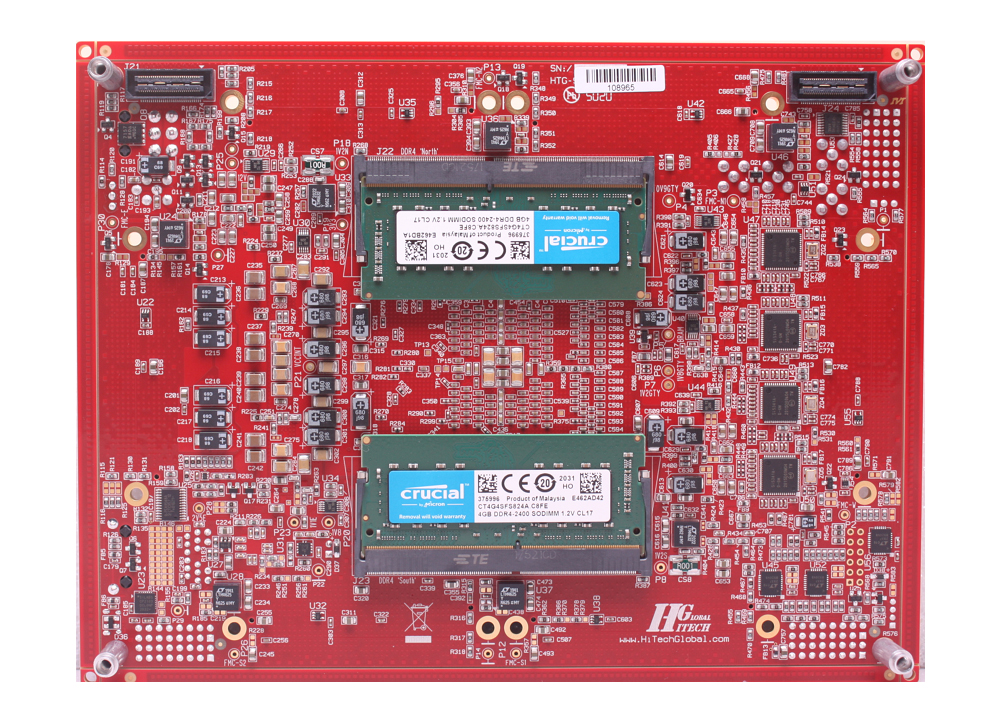

FPGA prototyping of digital functional blocks;

Functional verification of functional blocks on FPGA models;

Assembly and prototyping of SoC (system on chip) projects on FPGA.

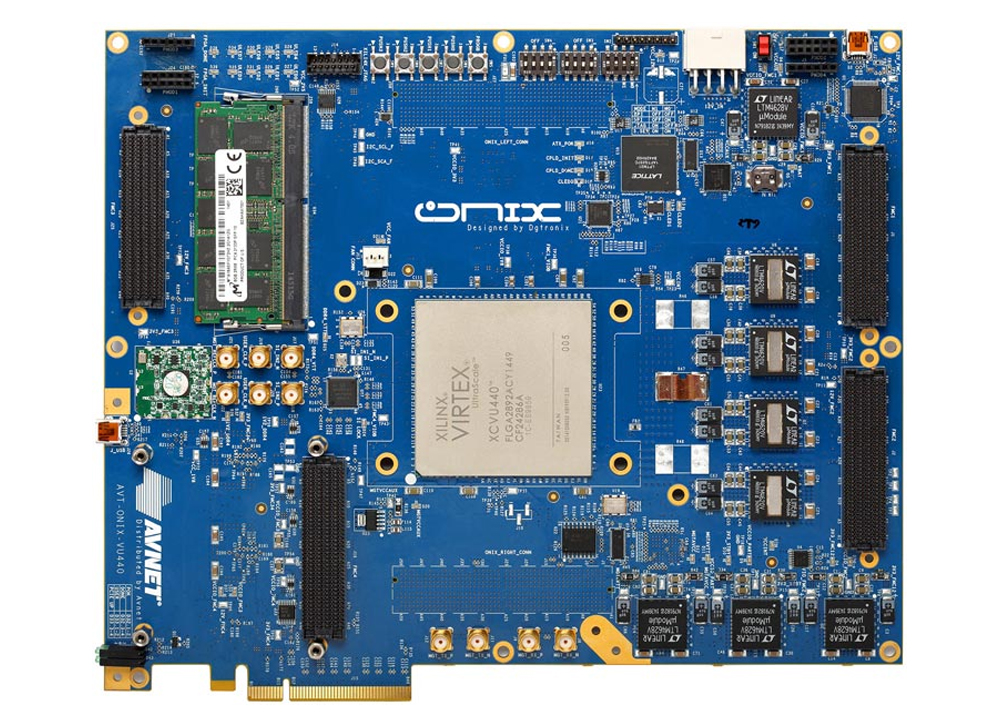

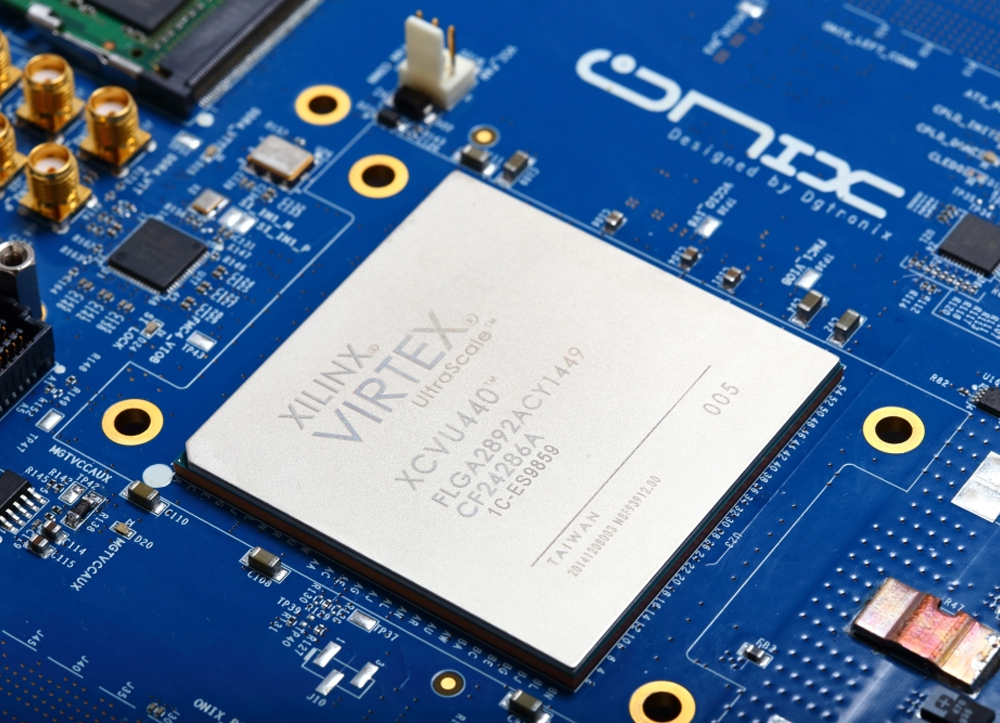

Boards for creating prototypes and validation platforms based on:

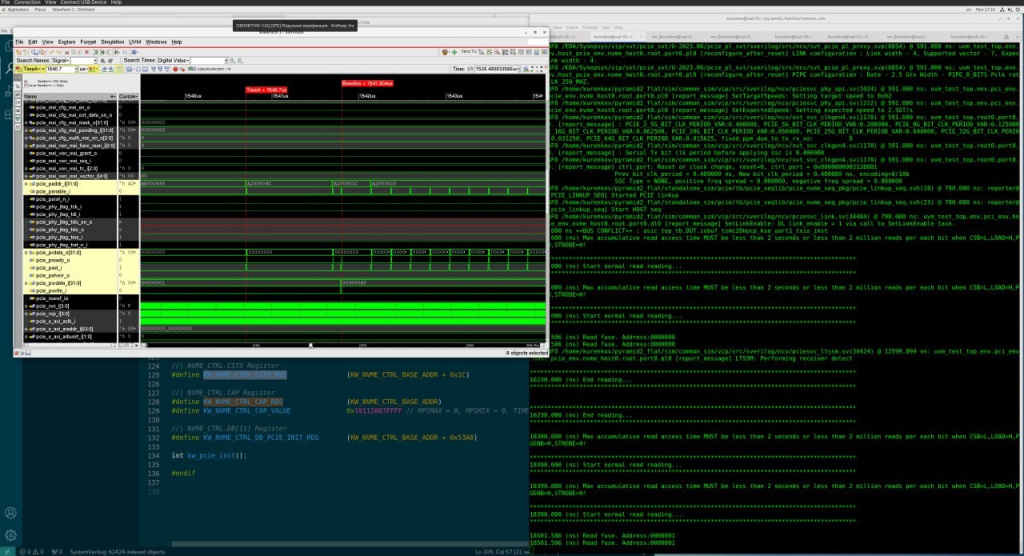

For the design and simulation of complex functional blocks, RTL code developers use both classical tools and specialized software packages developed in Russia. In particular, some functional blocks of projects are created using the software package for high-level hardware description language (HDL) “Integrated Circuit Development Toolkit (IRIS System)”. The authors of IRIS are researchers from the Mechanics and Mathematics Faculty of Lomonosov Moscow State University. The IRIS system is a completely Russian development, which allows for easy adjustments to its development vector and further integration into the stack of Russian microelectronics development tools.

The undeniable advantages of the IRIS system include high development speed, the use of a programming language familiar to most developers, full compliance with industry standards, the system's self-sufficiency, and its good functional compatibility with popular development tools from other manufacturers.

The IRIS system is a high-level hardware description language (HDL) aimed at rapid creation and testing of complex hardware modules;

It is implemented as a C++ library, one of the most popular programming languages, for which there is a large selection of high-performance compilers (Visual Studio, GCC, CLang). The choice of the popular language C++ is especially important in this context, as it significantly lowers the entry threshold for most engineers who are already familiar with it;

The system has a built-in ultra-fast simulator, allowing users to avoid using external tools (Verilator, Questa Sim, Vivado, etc.) and working many times faster than the built-in Chisel simulator.

Creating a hardware model (RTL Verilog) is the most costly and time-consuming stage (1.5-2 years) in the design process. Numerous examples of using IRIS in designing complex chips have shown that design time is reduced several times.

The ability to create, debug, and simulate functional blocks in the IRIS development environment and produce debugged RTL Verilog code allows for a reduction in the number of commercial CAD tools used in the IC design workflow. For example, by using fully debugged RTL code, one can skip Verilog simulation with Xcelium (Cadence), VCS (Synopsys) and immediately proceed to the logical synthesis stage. The compliance of the generated netlist with the original RTL is verified using logical equivalence checking, which also allows skipping the Verilog simulation in the netlist.

The resulting Verilog description of the developed functional blocks meets the 1364-2005 standard - IEEE Standard for Verilog Hardware Description Language (files with .v extension), allowing the use of various versions, including the most modern, of logical synthesis tools such as Genus (Cadence), Design Compiler (Synopsys), Vivado (Xilinx). To observe timing diagrams, IRIS generates files in the standardized Value Change Dump (VCD) format, defined in the IEEE Standard 1364-2001 (with .vcd extension). If necessary, this gives the developer additional opportunities to connect and use visualization in simulation tools like Xelium (Cadence), VCS (Synopsys).

Development of software code, HDL descriptions using programming languages C, C++, Verilog/System Verilog family.

Development of software code for digital complex functional (CF) blocks for use in SoC, such as high-speed peripheral devices, blocks implementing complex mathematical encoding-decoding functions, and other algorithms.

Integration of project components at the top (TOP) level.

Development of controller configurations, implementation of controller and physical part interface links, formation of timing constraint files, calculation and substitution of memory blocks.

Conducting HDL simulation, logical synthesis, formal verification, physical synthesis, and final checks of design technology constraints to obtain the final GDSII file.

Implementation of Digital on Top Flow approaches.

Verification of developed Verilog RTL descriptions obtained through the translation of software code using the IRIS system.

FPGA prototyping of developed functional blocks based on Xilinx Ultrascale+ hardware.

Development of device models implementing the most significant set of core functions.

Since its establishment in 2022, the center has been systematically working on creating the design center infrastructure, which today includes storage systems, high-performance servers and FPGA stands, workstations, specialized software, and powerful computing equipment for various types of tasks (including high-performance CAD for FPGA and ASIC development).

The design center's equipment meets global standards and is unique, as it allows not only for the development of ICs, integrated circuits, and SoCs but also for comprehensive testing of the obtained technical samples under various types of loads.